So, nach fast 13 Jahren war es an der Zeit... meine gefrickelte C64 Transputer-Karte musste mal "in Schön" gemacht werden.

Und wie das so ist, wenn man schon mal dabei ist, dann könnte man doch noch dies und das... und vielleicht auch noch hier ein wenig...

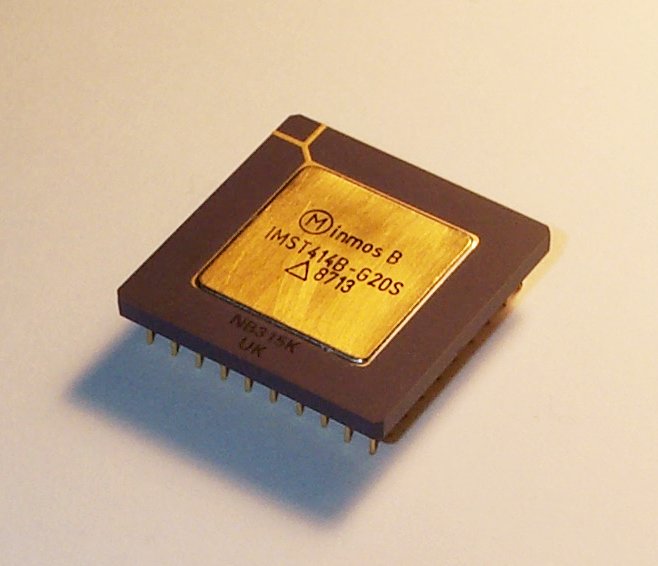

Herausgekommen ist die T2C= quasi "Eine für (fast) Alle".

Als (meines Wissens) erste 'Flipper Karte' für 8-bit Commies kann sie sowohl am C64, C128 als auch an der C264 Familie (C116, C16, plus/4) betrieben werden.

Einfach um 180° drehen und schwupp hat der Plus/4 bis zu 15 MIPS am port hängen 💪

Den kompletten Yadda-Yadda könnt Ihr bei Interesse hier nachlesen: https://www.geekdot.com/t2c/

PeterSieg: Solltest Du mal an eine Neuauflage Deines Buches denken, wäre das die Chance das Foto der hässlichen T2C64 auf S.139 zu ersetzen ![]()

| Ich pack' das hier nochmal dazu (auch wenn's auf der Webseite steht): Es gibt noch keine sinnvolle (?) Software dazu. Nur kleine Demos und Tool-Schnipsel. Die Genialität kommt mit Deiner Arbeit Dein Commodore wird keinen Fitz schneller durch die Karte. Erst wenn man code für den Transputer geschrieben hat und dieser mit dem Commodore daten austauscht, wird es schnell... ein Beispiel ist hier das Mandelbrot Fraktal, das der Transputer berechnet und der C64 (nur noch) darstellt. Denkbar wäre auch Kompression oder wilder Mathe-Kram. Weiterhin ist zu beachten, daß so ein TRAM auch ganz gut Strom ziehen kann. Mein C64, C128 und Plus/4 kommen alle mit dem Standard Netzteil klar. Aber da steckt auch nur ein TRAM mit 128KB drauf. "Your milage may vary" |