Vielen Dank für eure Antworten!

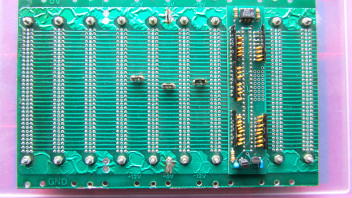

Da sind viele leere Sockel. Hast du eine Ahnung ob das ok ist?

Im ersten Platinensatz (lakosa_komplett.JPG) sind alle nötigen Chips vorhanden, diesen Platinensatz verwende ich zur Zeit. Ein leerer 20-Pin Sockel ist da, der soll aber tatsächlich leer sein da an diesem Sockel Port B des 8255 PPI ausgegeben wird.

Hast du mal geschaut, ob auf die DART zugegriffen wird (ChipSelect) ?

Bekommt die DART auch einen Takt?

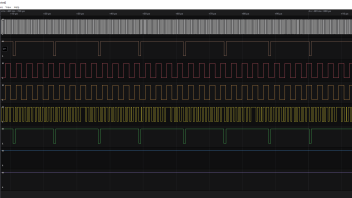

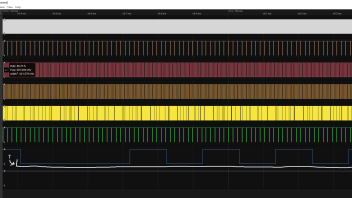

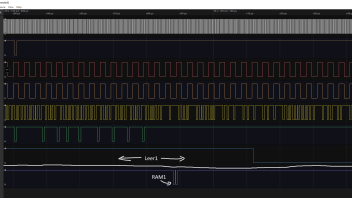

Das habe ich gerade eben gemacht. Auf den DART wird quasi ständig zugegriffen, und Takt haben auch beide Kanäle:

Auf den DART wird quasi ständig zugegriffen, und Takt haben auch beide Kanäle:

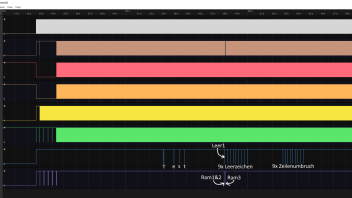

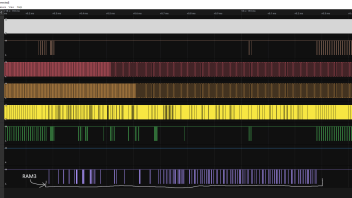

Ich hab das ganze mal beschriftet. Zuerst habe ich über das Terminal (9600 Baud, 8N1) "Test" gesendet, danach 9-mal Leertaste und 9-mal Enter gedrückt.

Nur auf das allererste Leerzeichen scheint der Computer zu reagieren (Jedoch nicht mit einer Ausgabe, ich habe TxDA und TxDB diesmal nicht überwacht, da bei identischen Versuchen zuvor auch kein Signal über TxDA oder TxDB gesendet wurde). Das zweite Bild zeigt eine Nahaufnahme während nichts besonderes passiert.

Beim drücken von "T" (oder "e", "s", "t" und Enter) scheint der Computer wohl auch nichts auffälliges zu machen.

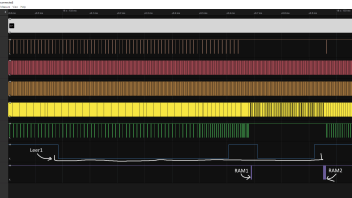

Bei dem ersten Leerzeichen hingegen wird dieses wohl vom Computer bemerkt, und auf das EPC-RAM zugegriffen.

Außerdem geschieht einige Zeit nach Ende des ersten Leerzeichens auch nochmal eine ganze Menge:

Eine Anmerkung zur Inbetriebnahme:

Die RTS- und CTS-Leitungen des DART werden auf die Interface-Platine geführt.

Vielleicht sollte man RTS und CTS brücken, weil das Monitor-Programm evtl. Hardware Flow Control programmiert hat.

CTS (Clear to Send; „Sendeerlaubnis“; Ein High-Pegel an diesem Eingang ist ein Signal der Gegenstelle (Terminal), dass sie Daten von DTE (Lakosa) entgegennehmen kann) habe ich schon gleich von Anfang an auf +5V gelegt (Ich habe es auch mal ohne Belegung probiert, auch kein Erfolg), RTS (Ready to Send; „Sendeanforderung“; ein High-Pegel an diesem Ausgang signalisiert, dass DTE (Lakosa) Daten senden möchte) unbestückt gelassen, da ich das Terminal ohne Flow-Control verwende.

Allerdings habe ich die Lakosa MPR-II CPU nie besessen.

Ich habe mir eine Z80 CPU-Karte selbst gefädelt und das notwendige Monitor-Programm

zum Laden des Betriebsssytems selbst geschrieben.

Ich glaube ich habe Bilder von deinem System auf oldcomputers-ddns.org gesehen, das Fädeln der EPC-Karte muss ja echt anstrengend gewesen sein, erstaunlich!

Die Floppy Disk Controller Platine scheint auch gleich zu sein.

Ich habe aber den Eindruck, daß das Projekt bei Lakosa noch in Arbeit war als ich die Platinen gekauft habe.

Auf meiner FDC-Platine gibt es nachgelötete Drähte für die Floppy Motor-Steuerung.

Leider funktioniert bei meinem System der Floppy Controller nicht mehr zuverlässig.

Meisten geht schon das Laden des Betriebssystems in die Hose.

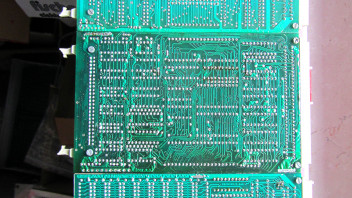

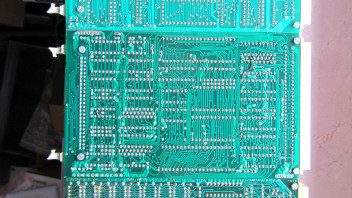

Ich habe meine mal genauer unter die Lupe genommen und auch bei diesen sind einige Fädeldrähte zu sehen. Ob die allerdings von Werk aus sind kann ich nicht sagen.

Ich würde mich über weitere Fotos der einzelnen Karten freuen.

Hat der Bekannte vielleicht weitere Unterlagen zu dem Lakosa Rechner retten können?

Außer diesen Platinen hat leider nichts mehr überlebt.

Fotos der Vorderseiten der Platinen habe ich oben bereits gemacht, hier nochmal die Rückseiten:

Ich muss mal gucken wann ich bessere Fotos machen kann, dazu muss ich hier erstmal wieder aufräumen und einen vernünftigen Platz und Hintergrund zum Fotografieren finden...

![]()