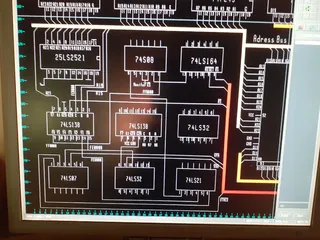

danke ! das Programm heisst iSMDB ( iSTEC META DATABASE ) . Das Programm ist eine eigene Entwicklung

aus der Zeit von 1993 - 2000 nach dem ich Computervision ( CV ) verlassen habe. Entwickelt auf SUN !, SUN 2 dann SUN Ultara Sparc 10.

es gab auch eine Portierung auf HP workstation nur fuer Siemens in Berlin. Ende der neunziger Jahre auch Portiert auf Windos (PC)

weil Kunden immer mehr von teuren Workstaion's auf PC Hardware umgestiegen sind.

Habe in 1993 meine eigene FA. gegruendet. iSTEC ( Inovative Software Technologien ) 1993 - 2006 mit Sitz in Muenchen.