Moin,

ich habe mich in letzter Zeit mit RAM-Upgrades für unsere kleinen Sonnen beschäftigt und festgestellt, daß da zu Ultra- und Blade-Zeiten doch so einige Fallstricke eingebaut sind ...

Sun Ultra 5/10 - hört sich erst einmal "machbar" an ...

- 168pin ECC buffered 3,3V, idealerweise 50ns (ab 360MHz sind 50ns ein Muß)

Das große ABER - die Module müssen mit 8k Refresh arbeiten, sonst wird nur das halbe RAM erkannt.

Auch spannend ...

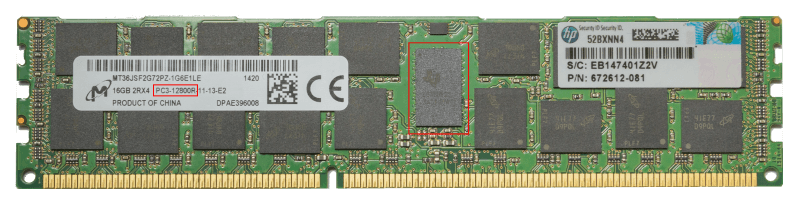

die SunFire V100/V120 benutzen 512MB 3.3V ECC PC133 SDRAM DIMM

Die Blade 150 hat 512MB 3.3V ECC 10ns PC133 SDRAM DIMM

Steckt man die V100er RAMs alleine in die Blade, werden sie nicht erkannt. Steckt man z.B. 2 "V" zu einem existierenden "Blade"; dann werden zwar im OBP 1536 MB erkannt - laufen tut die Kiste aber nicht mehr.

Hat noch jemand spannende Geschichten dazu?