Speicher satt

Ein Problem hat mich schon immer beim MFA gestört: Das Speicherbild bzw. der Umgang mit den verschiedenen Speicherkarten. Es gibt die Standard 8K-Karte die man in verschiedene Speicherbereiche einblenden konnte. Dann gab es irgendwann die 16K-Karte, und die Karten mit Boot-EPROM.

Bei all diesen Karten musste jeweils genau darauf geachtet werden welche mit welcher kombiniert und an welchen Speicherbereich diese jeweils aktiv war.

Eine Idee

Die ersten Ideen einer flexibleren Speicherkarte waren relativ schnell geboren. Sie sollte die vollen 64KB abdecken und wenn möglich sogar mehr über ein noch zu entwerfendes Banking-Verfahren. Auch die Boot-Eprom-Funktion sollte irgendwie realisiert werden. Es wäre auch echt cool wenn man das System Inplace editieren könnte, denn gerade in meiner frühen Jugend habe ich da schon öfters ein paar Änderungen vorgenommen und dazu immer wieder Eproms brennen macht ja irgendwie keinen Spaß.

Für die Auswahl des Paging-Bereiches kamen verschiedene Ideen in Frage. Allen voran über einen Out-Befehl. Doch hier wäre vermutlich irgendwann das Problem aufgetreten, dass es zu Überschneidungen bzw. Überlappung mit bestehenden Interfacekarten kommen könnte. Andere Alternativen mit PAL-Chips wurden ebenfalls verworfen, da aktuell weder entsprechende Programmierumgebung vorhanden ist, noch ausreichendes Know-How und der Charme des MFA hätte vermutlich darunter leiden können. Auch das jederzeitige Auslesen sollte irgendwie machbar sein.

Heraus kam eine direkte 16-Bit Speicheradressierung die einstellbar ist. Durch das Schreiben in eine Speicherzelle wird die entsprechende Paging-Seite in einen einstellbaren Speicherbereich eingeblendet. Durch das Schreiben und Lesen in die Speicherzelle kann diese im Programmcode jederzeit wieder in Erfahrung gebracht werden.

Auch eine Anzeige der aktuellen Paging-Seite wäre nett, und so kommt nun auch eine 7-Segment-Anzeige mit auf die Platine.

Die erste Ideen-Skizze:

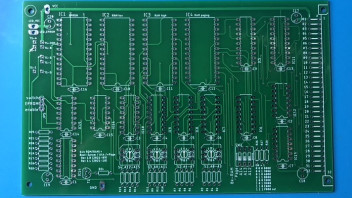

Der erste Entwurf der Platine, der eher einem Prototyp gleicht. Denn dieser hatte 3 grobe Layout und Schaltungsfehler und war noch nicht so richtig perfekt.

Peinlichkeit 1: Bei der Anzeige-LED zum aktiven ROM wurde doch glatt der Vorwiderstand vergessen.

Peinlichkeit 2: Beim Verdrahten des 7486 habe ich das falsche Signal genommen und musste dann nachträglich ein paar Leitungen durch einen freien Inverter jagen und das Layout ein wenig "umorganisieren".

Die überarbeitete Version der RAM/ROM-Paging-Karte

Die fertige (korrigierte) RAM-Karte

Die Frontblende mit Anzeige-LED und Schalter für das manuelle aktivieren des EPROMs

Die Speicherkarte in Betrieb (hier Paging-Seite 7 ausgewählt)

Funktionsbeschreibung der Karte

Grundsätzliches

Die Karte besteht im wesentlichen aus vier 32kb Speicher-Chips (27256 und 2 x 62256 o.ä.). Ein zusätzlicher 32KB RAM-Chip ist das Paging-RAM.

Paging-Funktion

Der zusätzliche Paging-RAM-Chip (IC4) wird in 8 jeweils 4kb-Seiten in den vorhandenen MFA-Speicherbereich 8000 - E000 eingeblendet. Der gewünschte Bereich ist dabei über den DIP-Schalter SW1 auswählbar. Achtung: F000 macht beim MFA wenig sinn, denn dieser Bereich ist ja vom System belegt, unter anderen der Stack.

Die Auswahl der gewünschten Seite wird über einen Memory-Write-Befehl auf eine, über die Hex-Drehschalter (S1-S4) einstellbare, 16-Bit-Adresse vorgenommen. Über folgenden Code wird eine Seite des RAM-Paging aktiviert:

MVI A,03h ; Seite 3

STA 0FE00h ; In die per Schalter eingestellte Adress-Selektionsadresse schreiben

Dadurch dass hier gleichzeitig geschrieben wird (Pageselektor-Chip IC11 und System-Speicher) kann jederzeit die gerade aktuell eingestellte Paging-Seite wieder in Erfahrung gebracht werden.

Boot-Rom-Funktion

Die Boot-ROM-Funktion bzw. das Abschalten des EPROM erfolgt, wie beim Original auch, durch einen Lesebefehl auf eine Adresse im Bereich 8000h - BFFFh. Ein aktives EPROM wird zusätzlich über die grüne LED an der Frontblende angezeigt.

Da auch hier der untere Speicher parallel zur Verfügung wird, kann bei aktivem EPROM in den Speicher 0000h-7FFFh geschrieben werden. Dies kann man dafür nutzen, über ein den KMD+> - Befehl Copy den gesamten Bereich von 0000h-7FFFh in den Bereich 0000h zu kopieren und anschließend mit einem Lesebefehl auf Adresse >= 8000h das EPROM zu aktivieren. Nun befindet man sich dann mit dem MAT-System im RAM. Das hat den Vorteil, nun kann man Inline am Systemcode herumspielen.

CP/M macht's vor

Dadurch dass das gesamte MAT85+-System zur Verfügung steht, sind auch alle Floppy-Funktionen vorhanden. Somit kann man sein MAT85+-System, das man sich vorher auf Diskette gespeichert hat, nun im "Boot-Vorgang" in den Speicher laden, auf RAM umschalten und durchstarten. Da die Datei sich den Startbereich ja gemerkt hat, muss man dazu nicht mehr viel auswählen, außer dem gewünschten Dateinamen (sprich "OS"-Variante).

Entdeckte Fehler

Bei der ersten Inbetriebnahme ist nach dem Einschalten immer wieder das EPROM abgeschaltet worden und das System lief buchstäblich ins leere.

Erst nach einiger Suche und Einzelschrittmodus des Startvorganges (waren schon einige Schritte die das System durchführt bevor da was passierte) ist ein "Bug" des Systems aufgefallen. Dazu ein Auszug dem dem MAT85-Quellcodes:

191 RESET: LXI SP,MONSTK ;STACK INITIALISIEREN

192 CALL BPTREM ;Breakpointtabelle löschen <-- ? Warum jetzt schon ?

193 CALL CASINIT ;CASSETTEN I/O INITIALISIEREN

194 MVI A,$C3

195 STA SERIN ;ADRESSEN DER SERIELLEN ROUTINEN VORBESETZEN

196 STA SEROUT ;MIT DEN NORMALEN ROUTINEN

197 LXI H,SERI

198 SHLD SERIN+1

199 LXI H,SERO

200 SHLD SEROUT+1

201

202 LXI H,RESBUF ;POWER UP ODER WARMSTART ?

203 MVI A,$5A

204 CMP M

205 JZ TASTERRESET ;WARMSTART, RAM IST SCHON INITIALISIERT

206 MOV M,A ;POWER UP, BZW. KALTSTART

207 LXI H,BRAM ;RAM INITIALISIEREN (=0 SETZEN)

208 MVI C,ERAM-BRAM

209 RESET2: MVI M,$0

210 INX H

211 DCR C

212 JNZ RESET2

213 LXI H,USRSTK ;ANWENDER-STACK INITIALISIEREN

214 SHLD SPWERT

215 MVI A,'H'

216 STA FORMAT ;FORMAT = HEX

217 CALL SERINIT ;SERIELLEN I/O INITIALISIEREN

218 CALL LBINIT ;LABELTABELLE LOESCHEN

219 CALL WCRLFI

220

221 .text 'BFZ-MONITOR VERSION 1.8',LF,$0

222

223 CALL HELP ;ALLE KOMMANDOS AUSDRUCKEN

Alles anzeigen

Die Zeile 192 müsste meines Erachtens an seiner Stelle entfernt und nach der Zeile 212 wieder eingefügt werden. Denn nach der Initialisierung des Systemspeichers (ab Zeile 208 ERAM-BRAM) darf er gerne seine Breakpoint-Tabelle löschen. Direkt nach dem Einschalten eine noch nicht initialisierte Breakpoint-Tabelle zu löschen, macht zum einen wenig Sinn und kann durchaus zu Schreib-/Lesevorgängen in einen Speicher >=8000h führen. Dadurch wird aber "aus versehen" das Boot-Eprom abgeschaltet. Da aber das parallele RAM noch keinen vernünftigen Code enthält, geht das schief und das System bleibt hängen (man könnte auch von einem Blue-Screen reden, das wäre gegenüber dem MFA aber fast eine Beleidigung ...  )

)

Erweiterungen

Nichts ist perfekt, so auch diese RAM-Karte. Derzeit sind folgende Erweiterungen geplant:

- Erweiterung auf 64KB Paging-RAM (Seiten 0-F)

Dazu muss ich aber noch ein wenig Platz auf der Platine schaffen oder die 62256 in der, nur schwer erhältlichen, schmalen Gehäuseform wählen oder in SMD ausführen - Batteriepufferung

Der komplette Speicher über eine Batterie (oder Akku) puffern. Ich verspreche auch, dass ich dafür keine Freileitungen verwende ...  MFA - Reaktivierung nach über 30 Jahren

MFA - Reaktivierung nach über 30 Jahren

Das hätte den Vorteil, dass das Betriebssystem nicht immer neu gebootet werden muss, z.B. bei Anpassungen am Programmcode (Löschtaste sollte aber noch vorhanden sein) - EEPROM-Unterstützung

Eventuelle Anpassungen zur Nutzung von EEPROM-Bausteinen

Wenn jemand noch weitere Ideen hat, gerne her damit. Wenn diese umsetzbar sind, kann die Karte ja nur noch besser werden.

---

Auch hier wieder wie gehabt: EAGLE-Projekt und CAM-Daten im Anhang.

Aktuell habe ich hier noch 1 Platine übrig. Wenn auch hier jemand Interesse daran hat, einfach melden.