Hallo alle zusammen!

Jetzt hat es dann doch etwas länger gedauert, bis ich meine Erkältung aus dem Urlaub auskuriert hatte. Aber jetzt ist der Kopf wieder frisch und ich kann mich endlich wieder ein wenig dem Basteln widmen.

Zunächst erst mal herzlichen Dank an NorbertJ und Dietrich für ihre Support Unterstützung zu den Fragen von discmix . Ich hoffe, Marco, du bist schon etwas weiter gekommen. Dennoch hier auch noch ein paar Anmerkungen zu deinen Fragen, auch wenn Norbert und Dietrich diese schon zum Teil oder ganz beantwortet haben.

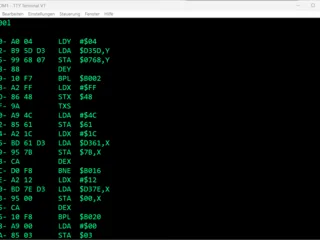

1. Basic ist im ROM der Language/IO Karte enthalten. Ohne diese Karte könntest du höchstens EhBasic via XModem auf den Rechner laden. Ich hab zwar diesbezüglich noch nichts vorbereitet, das wäre aber kein all zu großes Problem, wenn du Basic einfach mal ausprobieren möchtest. Allerdings sind dann einige Basic Befehle natürlich nicht ausführbar, da sie wiederum Hardware-Funktionen der IO Karte ansprechen.

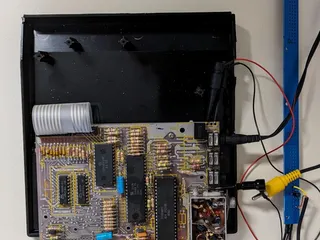

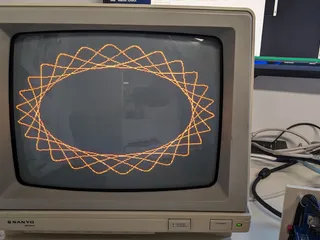

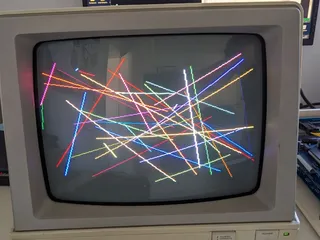

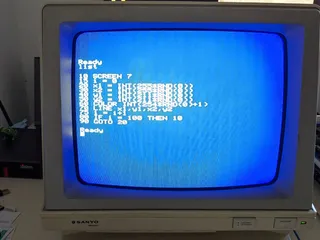

2. Der Floppy-/Graphics-Controller sollte unabhängig von der IO Karte laufen. ABER: Ich hab das bei mir auch vorhin nochmal getestet und tatsächlich initialisiert sich der Grafik Controller meist nicht richtig. D.h. eigentlich fast nie. Eher sporadisch wird nach dem Einschalten (aber nie nach einem manuellen Reset) dann mal Text auf dem angeschlossenen Bildschirm angezeigt. Das ist in sofern seltsam, da ich 100% bestätigen kann, dass das mal funktioniert hat. Hier muss also ein Problem mit der neuesten BIOS Version vorliegen. Ich werde mich da auf alle Fälle schnellst möglich damit beschäftigen.

3. Wenn der FGC dann ohne IO Karte wieder laufen sollte, dann musst du auf alle Fälle die PS/2 Buchse auch eingelötet haben. Denn nur hierüber kannst du dann ja den Rechner bedienen. Wenn du beim Einschalten oder nach einem Reset ein Terminal am JC2 angeschlossen hast, dann wird die Ausgabe hierüber gemacht und ein an der Grafikkarte angeschlossener Bildschirm bleibt schwarz.

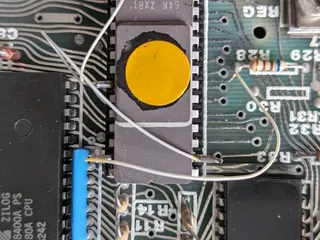

4. Du schreibst, dass dein Bildschirm immer ein weißes Bild bringt. Tatsächlich wird bei mir (bedingt durch den Fehler im BIOS) der Bildschirmspeicher nicht gelöscht und es werden wirre Zeichen und Klötzchen angezeigt. Ein vollständig weißer Bildschirm scheint mir da eher ein anderes Problem wieder zu spiegeln. Der bisher häufigste Fehler war ein Kurzschluss irgendwo an den Pins des Grafik Controllers V9938. Schau dir bitte da noch mal mit einer Lupe die Lötstellen genau an. Durch das halbe Rastermaß von 1,27 mm reicht da schon eine winzige Lötperle, um hier den Controller zu stören. Schau dir auch nochmal die Ausgangsstufen (Transistoren) des Controllers genau an. Auch hier könnte ein Kurzschluss das Problem verursachen.

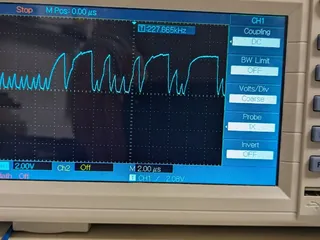

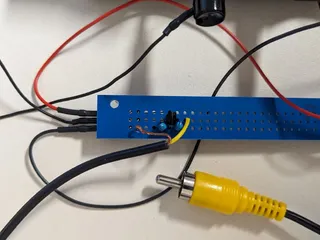

5. Schließ - wenn möglich - erst mal einen Composite Monitor an. Das ist schnell erledigt und du sparst dir das Löten eines geeigneten Video Kabels. Die Belegung an der RGB Video Buchse ist die gleiche, wie an einem Commodore 1083S Monitor. Hier kannst du also ein 1:1 Kabel mit beidseitigen Steckern anschließen. Der "VGA" Anschluss ist tatsächlich etwas irreführend - sorry. Die an diesem Anschluss liegenden Signale sind VGA komplett, d.h. R,G,B, H-Sync und V-Sync. Allerdings liegt die Zeilenfrequenz hier bei etwa 15KHz. Ein VGA Monitor hat hier eine Frequenz von etwa 31kHz. Deshalb könnte hier nur ein alter Multisync Monitor wohl ein Bild anzeigen, wenn dieser noch die CGA Auflösungen kann. EGA liegt hier bereits bei etwa 21kHZ.

6. Der Anschluss Floppy-Power liegt sehr nahe am eigentlichen Floppy Anschluss. Daher wird es hier recht eng, wenn du da einen entsprechenden Pin Header einbauen möchtest. Vorgesehen war hier von mir aber eher, dass man an dieser Stelle direkt die Kabelenden eines Floppy Spannungsversorgungssteckers einlötet. Ich hab bei mir aber jetzt direkt an der Backplane ein PC ATX-Netzteil angeschlossen, das ja sowieso gleich die Versorgungsstecker sowohl für 5 1/4" als auch 3 1/2 " Floppys mitbringt.

7. JP1 am Junior ][ ist der Jumper, um den Onboard Adress Decoder zu deaktivieren. Steht dieser auf EXT (Pin 2-3) dann läuft der Junior nicht. Hier musst du also Pin 1-2 verbinden. Der EXT Anschluss war auch am original Junior Computer schon drauf, um eben einen externen Adressdecoder zu realisieren, der dann ein anderes RAM/ROM/IO Mapping ermöglicht.

8. Norbert hatte mich nach der API für den Grafik Controller gefragt. Die reiche ich irgendwann heute Nachmittag noch nach, da ich jetzt erst mal wieder weg muss.

9. Danke an Dietrich, dass er die MKBOOT verbessert hat. Das hat mir wirklich wieder viel Arbeit abgenommen.

Gerade festgestellt, das ich STEP auf ON gesetzt hatte...die Ganze Zeit...AAAHHHHHHH ich werd nich mehr!!!

![]() .

.![]()