Ich hätte gerne alt & "original".

Danke!

Ich hätte gerne alt & "original".

Danke!

1x oldram Zitrus

1x oldram Richi

1x newram Toast_r

1x newram Holger

1x newram detlef

2x Oldie

1x CBM_Ba

1x Shadow-aSc board only

1x joshy

---

Warteliste

2x klaly (sorry ich hab Richi vorgezogen, weil er mich damals mit der Low Speed Graphik sehr geholfen hat)

2x newram und oldram cethewe

1x newram DL8EBD

1x detlef

bom

Ich freu mich so! ![]()

Gerne für mich die Version mit altem oder neuem RAM. Alt ist sicher „echter“- aber eben auch teurer.

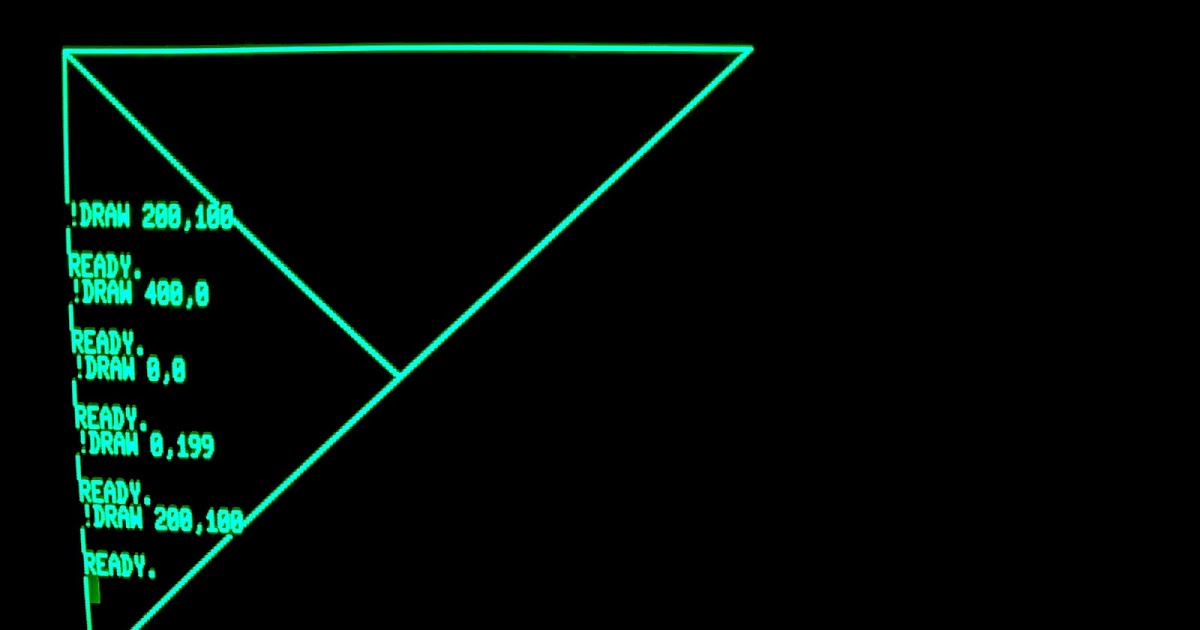

Es wird ein graphisches Fest wilder Grafiken, werte CBM-Jünger!

Halöle,

> Warteliste

> 2x klaly (sorry ich hab Richi vorgezogen, weil er mich damals mit der Low Speed Graphik sehr geholfen hat)

Warum steht da 2x bei mir ?

Ich brauche nur einen Board Satz, optimiertes RAM Board.

Wer wie wann vorgezogen wurde ist für mich irrelevant.

mfG. Klaus Loy

bom

Die HTML BOM ist ja mal richtig klasse. ![]()

Kannte ich noch garnicht.

1x oldram Zitrus

1x oldram Richi

1x oldram CBM_Ba

1x newram Toast_r

1x newram Holger

1x newram detlef

2x Oldie

1x Shadow-aSc board only

1x joshy

---

Warteliste

1x newram klaly

2x newram und oldram cethewe

1x newram DL8EBD

1x detlef

Moin,

ist es ok wenn ich sage mir ist egal welcher RAM ?

Hauptsache komplett. und einsatzfaehig ![]()

Toast_r

guckst Du:

Auf der Warteliste bitte auch mit newram-Board.

Ich habe aus dem Schaltplan noch nicht herauslesen können, ob die Data Becker Karte ein Speicherfenster irgendwo im Adressraum einblendet und wie groß das ist. Ich habe den Schaltplan ehrlich gesagt überhaupt noch nicht verstanden.

Ich habe mal ins ROM geschaut. Ein Speicherfenster gibt es nicht. Der Zugriff erfolgt über einige wenige IO-Adressen im Adressbereich E88x.

Das ist also nicht so sonderlich schnell. Aber ich glaube, meine Grafikkarte für den 3032 hat das damals auch so gemacht.

Es gibt ja auch beim CBM kein größeres freies Speicherfenster, wo man irgendwas einblenden könnte. Sonst verliert man gleich einen ganzen ROM-Erweiterungsbereich. In diesem Fall auf $9000.

An die, die das Schaltplan-Review gemacht haben: Wie funktioniert die Adressierung des Grafik-RAMs vom CBM aus?

Ich habe im ROM die IO-Adressen E882, E888 und E88A gefunden.

Der CRTC liegt auf E880, E881.

Grafikram liegt ab $0010

- E880 and E881 enable the 6545 like in an ordinary 8032

- E882 writes the lo-byte of the graphics address

- E888 writes the hi-byte

- E88A writes 8 bits graphics the the RAM (screen-start at $0010

QUELLE: http://lc64.blogspot.com/2017/…h-data-becker-hi-res.html

Den Schaltplan finde ich auch verwirrend, zumal ich da wirklich nur mit Viertelwissen im Dunklen stochere.

Aber ein Blick in die Schematics des 8032 hat mir etwas geholfen:

Das Charrom sitzt nicht auf dem Datenbus des PET, seine Daten gehen direkt in ein Schieberegister und werden von da auf den Schirm geschrieben (so machts die HSG auch, da verstand ich das zum ersten mal).

Daher die "doppelte" Anbindung an die CRTC und Charrom Sockel.

Den Datenbus des RAMs (liegt an J3) kann man über U11/12 und U9 auf den Charrom Sockel und damit das VideoOut legen.

In das Ram schreibt man über den Datenbus des PET (abgegriffen am CRTC Sockel). U18 und U13 koppeln diese die Datenbusse PETseite und Ramseite.

Gleich noch ein kleines Manko im Schaltplan gefunden. OEa und OEb von U9 sind active low, das sollte ich im Symbol ändern, dann ist der Plan klarer und man erkennt dass U17a zwischen Charrom (high active CS3) und RAM-Datenbus (active low OEa und OEb) umschaltet.

Grafikram liegt ab $0010

- E880 and E881 enable the 6545 like in an ordinary 8032

- E882 writes the lo-byte of the graphics address

- E888 writes the hi-byte

- E88A writes 8 bits graphics the the RAM (screen-start at $0010

QUELLE: http://lc64.blogspot.com/2017/…h-data-becker-hi-res.html

Danke, das hat schon mal weitergeholfen.

Vor allem auch dieses Blockschaltbild:

Sowas wie BA1 und BA3 hatte ich gesucht, aber in deinem Schaltbild noch nicht gefunden. Muss ich gleich noch mal suchen.

Vielleicht bin ich gerade etwas blind aber ich finde in deinem Schaltplan nicht die Stelle, wo BA1 und BA3 in die Adresslogik mit eingehen.

Der Bereich E88X wird vom CS des 6845 selektiert.

Aber jetzt müssen ja noch die Adressen xxx2, xxx8 und xxxA dekodiert werden. ![]()

Ich muss zugeben, ich blick nicht wirklich easy durch. Warum müssen sie das?

Hast du mal geschaut, Die Adressbits des Charroms werden ja dekodiert. Deren Adressbus ist LSDx was der gelatchte Datenbus der Screen-Rams ist.

Auch mal auf dem RAMBoard geschaut?

Ich muss zugeben, ich blick nicht wirklich easy durch. Warum müssen sie das?

Sonst könnte man das Grafikboard nicht über 3 unterschiedliche Adressen ansprechen. Irgendwo muss es eine Dekoder-Logik geben, die anhand einiger Adressleitungen festlegt, welche Register unter welcher Adresse erreichbar sind.

Durch den CS des CRTC wird die Basisadressse E88x festgelegt. Jetzt muss man aber noch die einzelnen Register dekodieren

A3 A2 A1 A0

0 X 0 X = 0 CRTC

0 X 1 X = 2 graphic address low

1 X 0 X = 8 graphic address high

1 X 1 X = A write dataA0 und A2 werden nicht verwendet. Das heisst die Register sind auch noch auf anderen Adressen gespiegelt.

Ich habe die jetzt mal beim Dekodieren als 0 angenommen.

Die vollständige Tabelle müsste dann so aussehen:

A3 A2 A1 A0

0 0 0 0 = 0 CRTC Regs

0 0 0 1 = 1 CRTC Data

0 0 1 0 = 2 graphic address low

0 0 1 1 = 3 graphic address low gespiegelt

0 1 0 0 = 4 CRTC Regs gespiegelt (?)

0 1 0 1 = 5 CRTC Data gespiegelt (?)

0 1 1 0 = 6 graphic address low gepiegelt

0 1 1 1 = 7 graphic address low gepiegelt

1 0 0 0 = 8 graphic address high

1 0 0 1 = 9 graphic address high

1 0 1 0 = A write graphic data

1 0 1 1 = B write graphic data

1 1 0 0 = C graphic address high

1 1 0 1 = D graphic address high

1 1 1 0 = E write graphic data

1 1 1 1 = F write graphic dataMechanische Frage zitruskeks :

Hast Du eigentlich das Rastermaß der Steckverbinder zwuschen Haupt- und RAM-Platine beibehalten, so daß die zwischen Original und Nachbau austauschbar wären?

Nicht daß das wichtig wäre - Nur interessehalber, da ich ja das Original hier habe. Wenn die im Maß zusammenpassen würden, würde ich nämlich auch die gedrehten Stift- und Socklelleisten verwenden, damit das zusammenpasst - sonst die günstigeren, stabileren mit den quadratischen Pins.

Zu den Bauteilen:

Ich habe fast alles da, mir fehlen nur ein paar Kleinigkeiten. Da ich sowieso noch ein paar Dinge brauche, mache ich gerade eine Bestellung bei Reichelt für den Rest fertig. Leider haben die offenbar nicht die 24poligen Schneidklemm IC-Adapter. Oder hat die da jemand gefunden?

Und noch zur Schaltung:

Das neue RAM-Board hat ja den doppelten Speicher. Die höchstwertige Adressleitung liegt jetzt einfach auf GND, so daß das erstmal nicht nutzbar ist. Hat sich da schon jemand so in die Schaltung eingearbeitet, daß er eine Idee hat, ob da irgendwo in einem Register noch ein Bit frei ist, das man zur Umschaltung nutzen könnte?

Die grüne Strippe ist auf dem 8032-Mainboard mit UD3 Pin5 zu verbinden.

Die weiß-blaue Strippe unter dem 7416 kommt an J4 Pin 23 (RDY).

Die unter Pin 1 vom 74LS00 kommt an J9 Pin 23 (R/W).

Die unter Pin2 vom 74LS00 kommt an J9 Pin 21 (PHI2).

Könntest du das bitte noch mal checken? Wenn du dich bei J9 vertan und von der falschen Seite gezählt hättest, dann wären das genau die von mir gesuchten Signale BA1 und BA3 (statt R/W und PHI2).

Wenn die originale 2.54er Raster (bzw der Databus-Slot sitzt auf der Hälfte) besitzt sollte sie passen.

Generell hab ich versucht alle Bauteile abgezählt auf das Raster an der identischen Stelle hinzupacken.

"

There are two wires to BA1, BA3 to decode the graphics registers.

Also there are wires to UD3 QA (8MHz) and to RDY of the CPU

"

Dann sollte ich das mal im Schema ändern. Am Board selbst ändert sich zum Glück nix.

Dann kapier selbst ich das langsam xD

Uhrgs... Von der falschen Seite gezählt. ![]()

Uhrgs... Von der falschen Seite gezählt.

Ich wäre hier jetzt wirklich verzweifelt, wenn das nicht so gewesen wäre. ![]()

Und noch zur Schaltung:

Das neue RAM-Board hat ja den doppelten Speicher. Die höchstwertige Adressleitung liegt jetzt einfach auf GND, so daß das erstmal nicht nutzbar ist. Hat sich da schon jemand so in die Schaltung eingearbeitet, daß er eine Idee hat, ob da irgendwo in einem Register noch ein Bit frei ist, das man zur Umschaltung nutzen könnte?

Was ist eigentlich mit den ungenutzten Adressleitungen MA10 und MA11 des CRTC?

Könnte man davon eine verwenden?

Hat jemand diese Mimik hier verstanden? Die Adressleitungen des Character-ROMs sind Eingänge. Warum sind die mit den Eingängen von Invertern verbunden?

Mein erster Gedanke war, dass im Schaltplan vielleicht der Sockel vom Character-ROM mit dem Sockel für den Flachbandverbinder zum 8032-Board verwechselt wurde. Dann wären die Adressleitungen Ausgänge. Aber es macht doch dann auch keinen Sinn, dass die Adressleitungen alle per Wired-OR zusammengeschaltet sind. ![]()

Achso, Denkfehler von mir. Über die Labels sind die Adressleitung vom ROM und dem Sockel ja zusätzlich noch verbunden.

Die Adresssignale kommen also vom Sockel und gehen an das ROM und an die Inverter.

Aber was machen die Inverter?

Open Collector als poor mans OR?

Open Collector als poor mans OR?

Ja, aber wozu? Was ist die Funktion dahinter?

Wenn das Daten wären, könnte ich mir das irgendwie vorstellen. Aber Adressleitungen?

Das dürfte die Funktion sein, die Text und Grafik überlagert.

Die Grafik wird nur da angezeigt, wo im Bildschirmspeicher ein Space steht, sonst wird das Zeichen aus dem Chargen angezeigt.

Achso, man kann Grafik und Text nicht beliebig mischen, weil dem CBM die Grafik über den Character-Generator untergeschoben wird.

Ok, dann ist mir das klar.

Bei meiner 3032-Grafik damals hatte ich in einigen Programmen spaßhalber die Pünktchen der Umlaute als Grafik-Punkte erzeugt. Sowas geht dann hier natürlich nicht. ![]()

Wieder was gelernt ![]()

Man erkennt das ja hier auf den Fotos. Aber der technische Hintergrund war mir nicht klar.