+ innen....

Junior Computer ][

-

-

danke

-

-

Funktioniert der Junior denn wieder?

-

Hallo, ja er lebt, er LEBT! 😊

-

Hallo zusammen, jetzt muss ich mich doch mal wieder melden und die neuesten Projektfortschritte mitteilen.

Ich hab letzte Woche begonnen mit dem von UTSource bestellten GM82C765B Floppy Disk Controller rum zu experimentieren und war da zu mindest Teilerfolgreich.

Der Chip ist von den Schnittstellen gesehen nicht allzu schwer anzuschließen und benutzt nur vier Hardware Adressen. Bei mir erstmal :

$800 : Read Only - Master Status Register

$801 : Read/Write - Data Register

$802 : Write Only - Disk Control Register (DCR)

$803 : Write Only - Disk Option Register (DOR)

Ich hatte zunächst nur das Problem, dass ich übersehen hatte, das die Reset Leitung des Chips nicht wie beim 6502 invertierend ist, und als R/W Leitung hatte ich zunächst RAM-R/W angeschlossen, was den Chip (besser gesagt das angeschlossene 5 1/4" Laufwerk) zum Stottern brachte. Ausserdem mussten einige

Manche Befehle wie SEEK und RECALIBRATE beenden mit einem Interrupt des FDC, der dann durch den Befehl SENSE INTERRUPT STATUS abgeschlossen werden muss. Da ich keine Interrupt Routine nutzen, sondern lieber alles per Polling machen möchte, habe ich die INT Leitung des FDC mit 74XX Logik als Pseudo-Register über das DOR gelegt, welches ja Write Only ist. Durch Lesen der Adresse $803 kann nun der INT Status ($80 = INT, $00 = kein INT) gelesen werden.

Mein größtes Problem ist zur Zeit, dass die einzelne Eingabe der Befehlsbytes über den System Monitor zwar korrekt abgearbeitet werden, eine Programmgesteuerte Übertragung aber nicht funktioniert, obwohl ich die angegebenen Wartezeiten von 12uS zwischen den Datenbytes einhalte und auch immer brav das Master Status Register zwischen jedem geschriebenen/gelesenen Datenbyte anschaue.

Hat da von euch schon jemand Erfahrung mit der Programmierung des GM82C765B, bzw. des Pin- und Befehlskompatiblen WD37C65C auf einem nicht x86 System gemacht. Ich hatte früher schon unter DOS den Floppy Controller öfters direkt angesprochen und war da eigentlich nie auf solche Probleme gestoßen. Eventuell habe ich da dann doch ein Hardware Timing Problem? Ich werde euch mal den aktuellen Schaltplan mit KiCAD erstellen, vielleicht findet ja irgend jemand einen totalen Bock in meiner bisherigen Schaltung.

Bzgl. Timing: Per Polling bekomme ich die Daten bei einem READ TRACK nur vollständig gelesen, wenn die Datenrate bei 250 kb/s MFM liegt. Dann hat die CPU 24 us Zeit ein einzelnes Datenbyte zu verarbeiten. Bei 500 kb/s sind es dann eben nur noch 12 us, was die 1MHz getaktete 6502 aber nicht hinbekommt. D.h. entweder ist die maximale Datenmenge auf einer Floppydisk dann eben auf 720KB beschränkt, oder ich bastele noch eine minimale DMA Schaltung mit Background Buffer an den FDC. Dazu würde ich dann aber ggf. auf ein GAL zurückgreifen, um nicht zu viele TTL Bausteinchen zu verbraten.

Ich werde das Thema jetzt aber erst mal wieder etwas zurückstellen, und mich wieder um den Command Interpreter für das M/OS 65 kümmern, so dass ich wenigstens mal ein DIR auf das SD-Karten Verzeichnis hinbekomme.

-

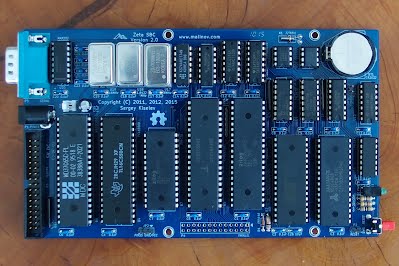

Den 37C65 hatte doch der Zeta V2 drin. Eventuell gibts bei den RomWBW Quellen da noch Tips oder Lösungsansätze?

Zeta SBC V2 - Malinov Family Web Presencewww.malinov.com

Zeta SBC V2 - Malinov Family Web Presencewww.malinov.com GitHub - wwarthen/RomWBW: System Software for Z80/Z180/Z280 ComputersSystem Software for Z80/Z180/Z280 Computers. Contribute to wwarthen/RomWBW development by creating an account on GitHub.github.com

GitHub - wwarthen/RomWBW: System Software for Z80/Z180/Z280 ComputersSystem Software for Z80/Z180/Z280 Computers. Contribute to wwarthen/RomWBW development by creating an account on GitHub.github.comGruß Jörg

-

Den 37C65 hatte doch der Zeta V2 drin. Eventuell gibts bei den RomWBW Quellen da noch Tips oder Lösungsansätze?

Hallo felge1966 , ich hatte befürchtet, dass jemand mit dem Verweis auf den Zeta V2 kommt. Den Code hab ich mir auch schon angesehen, allerdings bin ich überhaupt nicht in Z80 Code drin, und wollte das auch weitgehendst vermeiden mich da irgendwie durch zu wurschteln. Ist aber natürlich eine Option. Auf alle Fälle trotzdem vielen Dank für den Tipp.

Hier übrigens mal der minimale Schaltplan. Der FDC ist jetzt nicht mit drauf, weil ich das Symbol erst noch für die KiCAD Bibliothek erstellen müsste. An die FDC Pins gehen die Label A0, /RD, /WR, /LDOR, /LDCR, /CS, RES und INT. Datenbus ist ja klar und die Floppy Seite ist erst mal Wurscht. Die DMA Schnittstelle hab ich auch nicht in Benutzung, daher ist Terminal Count (TC) einfach auf +5V gelegt. Der 74LS244 übernimmt die Rolle des Read Registers für das Interrupt Signal des FDC.

-

Weiss jetzt nicht, ob K2 schon mit Phi2 verknüpft ist.

Falls nicht, dann ist es der klassische Fehler, beim 6502 den "Phi2 high" als AND in die /CS Bedingung zu vergessen.

A0..A15 und R/W werden zusammen gültig BEVOR dann etwas später die Daten gültig werden und dann erst wird Phi2 high.

-

Bzgl. Timing: Per Polling bekomme ich die Daten bei einem READ TRACK nur vollständig gelesen, wenn die Datenrate bei 250 kb/s MFM liegt. Dann hat die CPU 24 us Zeit ein einzelnes Datenbyte zu verarbeiten. Bei 500 kb/s sind es dann eben nur noch 12 us, was die 1MHz getaktete 6502 aber nicht hinbekommt. D.h. entweder ist die maximale Datenmenge auf einer Floppydisk dann eben auf 720KB beschränkt, oder ich bastele noch eine minimale DMA Schaltung mit Background Buffer an den FDC. Dazu würde ich dann aber ggf. auf ein GAL zurückgreifen, um nicht zu viele TTL Bausteinchen zu verbraten.

Meines Wissens gibt es keine Software-Lösung um mit 1 MHz 500kBit/s zu verarbeiten.

Ich habe mal mit dem SO (Set overflow) des 6502 als DMA request Eingang herumgespielt, weiss aber nicht mehr wie das damals[tm] ausging.

Das ging ungefähr so:

; overflow clear

; warte auf DMA request:

bvc *

; verarbeite byte

letztendlich war dann ein MC6844 dran. Weiss aber nun nicht, ob Du den MC6844 alleine über den BUS an den 6502 dran bekommst, also ob es die passenden Signale auf dem Bus hat, um den 6502 anzuhalten.

-

Weiss jetzt nicht, ob K2 schon mit Phi2 verknüpft ist.

Falls nicht, dann ist es der klassische Fehler, beim 6502 den "Phi2 high" als AND in die /CS Bedingung zu vergessen.

A0..A15 und R/W werden zusammen gültig BEVOR dann etwas später die Daten gültig werden und dann erst wird Phi2 high.

Hallo Reinhard . Vielen Dank für die Info. /CS hab ich jetzt tatsächlich noch nicht mit PHI2 verknüpft. Da der FDC die Daten bei steigender Flanke des /WR Signals latched, hatte ich die Befürchtung, dass bei vorherigen inaktiv werden der /CS Leitung dann die Daten garnicht übernommen werden. Denn die PHI2 Phase endet ja vor einer Änderung von R/W. Ich hatte zuerst auch versucht den FDC mit der RAM_R/W Leitung zu steuern. Diese ist ja mit PHI2 verknüpft und würde somit theoretisch den Latch Zyklus mit Ende der PHI2 High Phase beenden. Das mochte der FDC aber garnicht.

Ich werde nachher mal testen, ob eine Verknüpfung von K2 mit PHI2 den Durchbruch bringt.

Ich habe jetzt mal zwischen den Read Data und Write Data Befehlen im Code ein 255ms langes Delay gesetzt. Damit funktioniert es. Ist also ganz klar ein Timing Problem.

Meines Wissens gibt es keine Software-Lösung um mit 1 MHz 500kBit/s zu verarbeiten.

Ich denke auch, dass das nicht möglich ist. Ein LDA imm braucht 2 Zyklen, ein STA abs,X 5. Dann noch INX, ein BEQ und dann noch der Vergleich auf einen Page Überlauf wegen der 512 Byte Blocks. Das ist in 12 Zyklen nicht zu machen.

Der MC6844 ist natürlich auch eine nette Variante. Den hatte ich garnicht auf dem Schirm, weil der in meinen Motorola Datenbüchern leider keine Erwähnung findet. Da schaue ich auch immer gerne mal rein, wenn ich was exotisches für 8 Bitter brauche. Ich fürchte aber, dass der DMA Controller recht schwer zu bekommen ist. Hast du da schon irgendwelche Erfahrungen gesammelt?

Hab mir jetzt das Datenblatt gezogen und werde das als Gute Nacht Lektüre durchlesen (man sind wir alle schräg

).

).Meine Überlegung eines einfachen DMA war, nicht den Hauptspeicher für den Transfer zu nehmen und somit evtl. die CPU anhalten zu müssen, sondern einen Ein-/Ausblendbaren Speicherbereich soz. offline mit den Daten via DMA Handshake und einem Adresszähler zu befüllen, bzw. davon zu lesen. Wenn die Daten dann im Buffer stehen, blendet man diesen dann per Bank Switching in den Hauptspeicher ein. Das müsste mit überschaubarem Aufwand machbar sein.

Letztlich wäre ich aber auch mit einer 720K Floppy schon zufrieden, DD Disketten hab ich noch zu genüge rumfahren.

Reinhard was hast du da für einen schönen Floppy Controller

. Der sieht mir sehr nach Apple // Steckkarte aus. Sehr nett

. Der sieht mir sehr nach Apple // Steckkarte aus. Sehr nett

-

Ja, war/ist für den APPLE ][. Ich weiss aber nicht einmal mehr, ob der von mir entwickelt war, oder ob ich da mithalf, oder überhaupt nicht.

Irgendwann war die Apple ][ Zeit vorbei und 4 MHz Z80 Systeme mit DMA die "Norm"

-

PS: ich denke (ohne jetzt das Datenblatt zu studieren), dass es wie bei den meisten ICs ist: die steigende Flanke von WR oder CS latcht die Daten, was auch immer zuerst passiert.

-

Ja, war/ist für den APPLE ][. Ich weiss aber nicht einmal mehr, ob der von mir entwickelt war, oder ob ich da mithalf, oder überhaupt nicht.

Irgendwann war die Apple ][ Zeit vorbei und 4 MHz Z80 Systeme mit DMA die "Norm"

Ich hab den Umstieg auf Z80 nie geschafft. Ich war da zu sehr 6502 vernarrt. Eine kurze 68000 Phase dann bin ich, was Assembler Programmierung anging, in das x86 Lager umgestiegen.

PS: ich denke (ohne jetzt das Datenblatt zu studieren), dass es wie bei den meisten ICs ist: die steigende Flanke von WR oder CS latcht die Daten, was auch immer zuerst passiert.

Ich hab jetzt gerade mal K2 über einen Tristate Treiber mit PHI2 (bzw. PHI1 wg. invertierter Freigabe) synchronisiert. Reinhard du bist genial. Es funktioniert!

Offensichtlich ist es tatsächlich egal, ob /CS oder /WR zuerst inaktiv wird. Die Daten werden jetzt sauber gelatched und mein Programm wartet brav nach einem SEEK, bis das INT Signal auf High geht, bevor es SENSE INTERRUPT STATUS aufruft.

Ich hatte mich tatsächlich schon zu Beginn gewundert, warum der FDC trotz fehlender PHI2 Verknüpfung funktionierte, da bei Änderung des R/W Signals am 6502 die Daten schon lange nicht mehr stabil sein müssen.

Herzlichen Dank Reinhard!

-

Bei z80 war es seinerzeit auch problematisch, wenn der Systemtakt zu niedrig war. In der U880 Technik war die Aussage, dass ca 2,5 MHz Takt bei Wait Betrieb erforderlich sind. Die 2MHz des Z1013 waren damals zu gering. Könnte also echt Probleme machen.

Gruß Jörg

-

Jetzt gerade mal eine kleine Routine laufen lassen:

- Initialisieren des FDC

- Setzen der Step Rate, Head Load/Unload Time

- Recalibrate

- Seek auf Track 70

- Recalibrate

läuft wunderbar. Fragt man sich nur, warum RECALIBRATE nur 77 Steps Richtung Track 0 fährt und nicht wie der uPD765 255. So muss man um sicher auf Track 0 zu stehen bei einem 80 Track Laufwerk immer zwei mal rekalibrieren. Seltsam...

Weiß eigentlich jemand, was die optimalen Einstellungen für Head Load / Head Unload Time sind? Es geht ja bei den neueren Laufwerken nur darum ein Head Jittering nach der Kopfbewegung zu verhindern. Da müssten doch 16 ms HLT und 2 ms HUT reichen?

Hier der geänderte Schaltplan. Bleibt die Überlegung das TTL Grab in ein GAL zu verfrachten. Wäre ja mittlerweile kein großer Stilbruch, da ja auch schon veraltete Technik.

-

TTL kann aber jeder nachbauen - auch ohne passenden "Brenner".

-

TTL kann aber jeder nachbauen - auch ohne passenden "Brenner".

Stimmt natürlich schon, aber mittlerweile hat hier im Forum wahrscheinlich jeder einen günstigen Minipro TL866A o.ä. für seine (E)EPROMS und damit sind dann z.B. auch GAL16V8 programmierbar.

-

Hallo Jörg,

Thema DMA, da hatte ich mal was cooles gesehen und eben wieder gefunden.

Zur Funktion RD/WR µC <--> FDC:

keine Ahnung, ob sich das mit 765 FDC Chip realisieren liese.

Die Schaltung ist aus einem Datenblatt für einen HD-Controller Chip.

Weil da die Daten ja noch schneller fließen müssen, geht das nur mit DMA.

Man müsste da sicher einges an Logik umändern, bzw. dazu bauen (GAL).Zur Funktion schreiben µC --> FDC:

1. Zähler löschen

2. Nutzdaten in RAM rein schreiben, Zähler incr, byteweise schreiben3. Zähler löschen

4. FDC Write Kommando geben,

5. jetzt müsste die FDC und extra logik RD Signale liefern und Daten holen, außerdem Counter INCR machen.

6. CMD Ende detektieren, fertig

Lesen FDC --> µC

1. Zähler löschen

2. Read Kommando absetzen3. FDC Chip und Logik bringen Daten in RAM

4. CMD Ende detektieren, fertig5. Zähler löscvhen

5. Daten aus RAM zum µC Speicher holen, byteweise, mit incr

Ob das überhaupt gehen könnte, weiß ich nicht, mir gefiel nur diese Schaltung, lokale DMA in lokalen Speicher.

Hier das Datenblatt des WD1010.pdfmfG. Klaus Loy

-

Hallo klaly . Das sieht genauso aus, wie ich mir das vorgestellt hatte. Ein extra Sektor Buffer der via DMA befüllt und dann vom Host eingelesen wird (bzw. umgekehrt bei einem Write). Danke für das Datenblatt. Ich werd mir mal Gedanken machen, wie und ob ich das in den FDC integrieren werde.

Heute Nacht dachte ich, dass es doch noch Probleme mit meiner FDC Schaltung gibt. Ich wollte den Drive Status abfragen - laut Datenblättern von WD und (Unlucky) Goldstar der Befehl $00) - was der Controller standhaft mit Unkown Command quittierte. Zu allem Unglück gab die manuelle Eingabe ein anderes Status Ergebnis zurück, als es die Programm gesteuerte Ausführung machte. Letztlich hab ich dann das Datenblatt des UPD765 zu Rate gezogen und den Befehlscode $04 ausprobiert...und tadaaa... der Drive Status wurde angezeigt.

Echt blöde, da hat WD ein fehlerhaftes Datenblatt rausgebracht und alle schreiben einfach ab. Das ist ja wie in der Grundschule!

Immerhin sind bei Goldstar die Bezeichnungen der Register richtig, die sind nämlich bei WD durchrotiert (MST = ST0, ST0 = ST1 ...).

Jedenfalls scheint die Schaltung jetzt zu tun, was man von ihr erwartet.

Ich bin aber auch nicht vom Fehlerteufel verschont geblieben. Im Schaltplan liegen am 2 zu 4 Decoder die Ausgänge in der Reihenfolge von oben nach unten bei Q0..Q3. Ihr müsst euch da aber die Reihenfolge Q3..Q0 vorstellen, da bei mir wie oben erwähnt ja das MST an $800, Data an $801, /DCR an $802 und /DOR an $803 liegen. Wird natürlich in der endgültigen Schaltung korrigiert.

-

Jörg,

für diese DMA-Schaltung mit lokalem RAM könnte es zu Problemen bei Formatieren kommen.

Weil der RAM hat z.B. 1kB als Sektor Buffer, aber beim Formatieren muss man evtl. alle Bytes des gesamten Tracks, ohne Unterbrechung übertrage, zumindes bei den WD177x Chips.

Bitte da aufpassen. -

für diese DMA-Schaltung mit lokalem RAM könnte es zu Problemen bei Formatieren kommen.

Da sehe ich kein Problem. Für die Formatierung benötigt man ja kein DMA. Du musst da ja nur für jeden Sektor im Track die benötigten Daten (ID, GAP3, etc) bereitstellen. Das kann man dann wieder Interrupt gesteuert, bzw. per Polling machen, da die Zeiträume zwischen zwei Anfragen des Controllers ja riesig sind. Ob der Controller irgendwas DMA gesteuert machen soll, kann ich ja per SPECIFY Befehl (Byte 3, Bit 0) angeben und so einzelne Befehle gezielt als non DMA ausführen.

-

für diese DMA-Schaltung mit lokalem RAM könnte es zu Problemen bei Formatieren kommen.

Da sehe ich kein Problem. Für die Formatierung benötigt man ja kein DMA. Du musst da ja nur für jeden Sektor im Track die benötigten Daten (ID, GAP3, etc) bereitstellen. Das kann man dann wieder Interrupt gesteuert, bzw. per Polling machen, da die Zeiträume zwischen zwei Anfragen des Controllers ja riesig sind. Ob der Controller irgendwas DMA gesteuert machen soll, kann ich ja per SPECIFY Befehl (Byte 3, Bit 0) angeben und so einzelne Befehle gezielt als non DMA ausführen.

Du musst aber trotzdem pro Sektor 4 Bytes rasch an den Controller senden, damit er das ID-Feld erzeugen kann. Aber das passt natürlich in einen z.B. 2kB DMA-Puffer stets hinein.

Code

Alles anzeigenThe processor must send new values for C, H, R, and N to the WD37C65C for each sector on the track. If FDC is set for the DMA mode, it will issue four DMA requests per sector. If it is set for the Interrupt mode, it will issue four interrupts per sector and the processor must supply C, H, R, and N loads for each sector. The contents of the R register are incremented by 1 after each sector is formatted; thus, the R register contains a value of R when it is read during the Result phase. This incrementing and formaning continues for the whole track until the FDC detects the index hole for the second time, whereupon it terminates the command. -

Heute Nacht dachte ich, dass es doch noch Probleme mit meiner FDC Schaltung gibt. Ich wollte den Drive Status abfragen - laut Datenblättern von WD und (Unlucky) Goldstar der Befehl $00) - was der Controller standhaft mit Unkown Command quittierte. Zu allem Unglück gab die manuelle Eingabe ein anderes Status Ergebnis zurück, als es die Programm gesteuerte Ausführung machte. Letztlich hab ich dann das Datenblatt des UPD765 zu Rate gezogen und den Befehlscode $04 ausprobiert...und tadaaa... der Drive Status wurde angezeigt.

Echt blöde, da hat WD ein fehlerhaftes Datenblatt rausgebracht und alle schreiben einfach ab. Das ist ja wie in der Grundschule!

Immerhin sind bei Goldstar die Bezeichnungen der Register richtig, die sind nämlich bei WD durchrotiert (MST = ST0, ST0 = ST1 ...).

Im Western Digital Datenblatt für den WD37C65A/B steht $04 drin, im Datenblatt für den WD37C65C $00 ... werde einer schlau draus

-

So, bisher erst mal letzte Version des Schaltplans für den Floppy Controller, inkl. des WD37C65B (GM82C765B) und Floppy Connector. Das Pseudo Register (Read DOR) zeigt jetzt dann an Bit 8 den Interrupt und an Bit 7 Disk Changed an.

Du musst aber trotzdem pro Sektor 4 Bytes rasch an den Controller senden, damit er das ID-Feld erzeugen kann. Aber das passt natürlich in einen z.B. 2kB DMA-Puffer stets hinein.

Das stimmt schon, aber da komme ich mit wesentlich weniger Befehlen aus nämlich jeweils nur LDA und STA, das sollte dann zeitlich kein Problem sein.

-

Besser ist das!

. Jetzt mal das TTL Grab gegen ein GAL 16V8 ausgetauscht.

. Jetzt mal das TTL Grab gegen ein GAL 16V8 ausgetauscht.ThoralfAsmussen : Ich denke, dass ich das auch so lasse. Falls ich mich entschließe eine DMA Schaltung mit einzubauen, benötige ich sowieso noch min. weitere 8 Bausteinchen (2x Zähler, 2x Adress Bustreiber, 2x Datenbus Transeiver, RAM, GAL) wenn ich dafür dann eben auch ein GAL nehme, sonst wesentlich mehr. Damit ist es dann sowieso egal, ob ein oder zwei PLDs auf der Platine drauf sind. Zusätzlich soll ja auch noch der Grafik Controller samt RAM mit drauf. Da möchte ich so viele TTLs wie möglich einsparen.

Eventuell werde ich aber auch zwei Versionen - eine mit GALs und eine nur mit TTLs - machen, dann kann jeder selbst entscheiden, was er aufbauen möchte. Das dann aber nur, wenn ich mich gegen DMA entschließe.

-

Ich halte die Nutzung von 2 GALs für absolut legitim, wenn man doch auch bereits ein SD-Karten- und ein Stepdown-Modul im Einsatz hat. Die Grafik wird bestimmt auch noch eine Menge Platz benötigen. Außerdem ist eine Fehlersuche relativ einfach und übersichtlich.

-

moin, moin,

Zwischenfrage - welches Tool benutzt ihr für die GAL Programmierung ?

mfG Werner

-

-

Danke,

scheint aber nur für AMIGA zu sein - schade.

Brauche was für DOS/Windows ...

mfG Werner